INNOVATIVE INTEGRATION

PCI32

| Card Type | Digital I/O card |

| Chip Set | Unidentified |

| Maximum Onboard Memory | 1024KB SRAM |

| I/O Options | 32-bit PCI slot |

| Hard Drives supported | None |

| Floppy drives supported | None |

| Data Bus | 32-bit PCI |

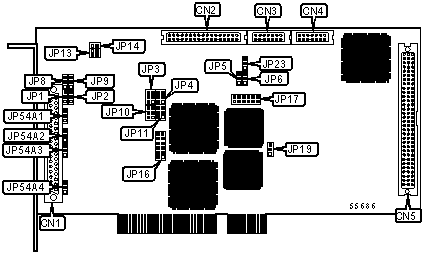

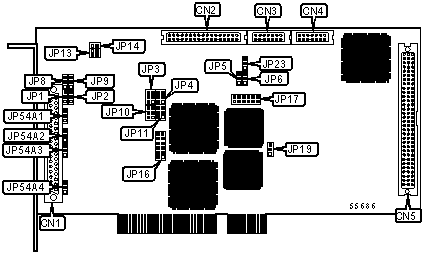

CONNECTIONS TABLE |

|||

Function |

Label | Function |

Label |

DB-37 connector |

CN1 | JTAG connector | CN4 |

| Digital I/O connector | CN2 | Memory expansion connector | CN5 |

| Sync serial connector | CN3 |

|

|

| USER CONFIGURABLE SETTINGS | |||

Function |

Label | Position | |

| » | 128KW 1 wait-state | JP19 |

Pins 1 & 2 closed |

| 512KW 1 wait-state | JP19 |

Pins 2 & 3 closed |

|

| » | AC 0 Output Range +/- 10V | JP1 | Pins 2 & 3 closed |

| AC 0 Output Range 0 - 10V | JP1 | Pins 1 & 2 closed | |

| » | DAC 1 Output Range +/- 10V | JP2 | Pins 2 & 3 closed |

| DAC 1 Output Range 0 - 10V | JP2 | Pins 1 & 2 closed | |

| » | DAC 2 Output Range +/- 10V | JP8 | Pins 2 & 3 closed |

| DAC 2 Output Range 0 - 10V | JP8 | Pins 1 & 2 closed | |

| » | DAC 3 Output Range +/- 10V | JP9 | Pins 2 & 3 closed |

| DAC 3 Output Range 0 - 10V | JP9 | Pins 1 & 2 closed | |

» |

JTAG Inverted Clock enabled | JP23 |

Pins 1 & 2 closed |

| JTAG Noninverted Clock enabled | JP23 |

Pins 2 & 3 closed |

|

DAC UPDATE TRIGGER SELECTION |

|||||

DAC Update Signal |

JP3 |

JP4 |

JP10 |

JP11 |

|

| » | TCLK0 driven | Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

Pins 1 & 2 |

| TCLK1 driven | Pins 3 & 4 |

Pins 3 & 4 |

Pins 3 & 4 |

Pins 3 & 4 |

|

| DSP memory access driven | Pins 5 & 6 |

Pins 5 & 6 |

Pins 5 & 6 |

Pins 5 & 6 |

|

A/D TRIGGER SELECTION |

|||

Settings |

JP5 |

JP6 |

|

| » | DSP timer 0 (TCLK0) or memory mapped | Pins 1 & 2 closed |

Pins 1 & 2 closed |

| DSP timer 1 (TCLK1) or memory mapped | Pins 2 & 3 closed |

Pins 2 & 3 closed |

|

| External clock or memory mapped | Open |

Open |

|

A/D POWER SELECTION: Channel 0 |

|||

Input Scan Range |

Register Setting |

JP54A1 |

|

» |

+/- 10V |

R17 = 10K |

Open |

0-10V |

R17 = 4.99K |

Pins 1 & 2 closed |

|

10-0V |

R17 = 4.99K |

Pins 2 & 3 closed |

|

A/D POWER SELECTION: Channel 1 |

|||

Input Scan Range |

Register Setting |

JP54A2 |

|

» |

+/- 10V |

R23 = 10K |

Open |

0-10V |

R23 = 4.99K |

Pins 1 & 2 closed |

|

10-0V |

R23 = 4.99K |

Pins 2 & 3 closed |

|

A/D POWER SELECTION: Channel 2 |

|||

Input Scan Range |

Register Setting |

JP54A3 |

|

» |

+/- 10V |

R29 = 10K |

Open |

0-10V |

R29 = 4.99K |

Pins 1 & 2 closed |

|

10-0V |

R29 = 4.99K |

Pins 2 & 3 closed |

|

A/D POWER SELECTION: Channel 3 |

|||

Input Scan Range |

Register Setting |

JP54A4 |

|

» |

+/- 10V |

R35 = 10K |

Open |

0-10V |

R35 = 4.99K |

Pins 1 & 2 closed |

|

10-0V |

R35 = 4.99K |

Pins 2 & 3 closed |

|

INTERRUPT INPUT COMBINATIONS: EI1 |

||

Setting |

JP17 |

|

| » | ADC 0/1 complete | Pins 1 & 3 closed |

| External digital clock | Pins 8 & 10 closed |

|

| PC interrupt 0 to DSP | Pins 1 & 2 closed |

|

INTERRUPT INPUT COMBINATIONS: EI2 |

||

Setting |

JP17 |

|

| » | ADC 0/1 complete | Pins 3 & 5 closed |

| ADC 2/3 complete | Pins 5 & 7 closed |

|

| External digital clock | Pins 10 & 12 closed |

|

| PC interrupt 1 to DSP | Pins 11 & 12 closed |

|

INTERRUPT INPUT COMBINATIONS: EI3 |

||

Setting |

JP17 |

|

| » | PC interrupt 0 to DSP | Pins 2 & 4 closed |

| ADC 0/1 complete | Pins 3 & 4 closed |

|

| PC interrupt 1 to DSP | Pins 9 & 11 closed |

|

| External digital clock | Pins 9 & 10 closed |

|

| ADC 2/3 complete | Pins 7 & 9 closed |

|

PARALLEL I/O PORT SELECTION |

||

Setting |

JP13 |

|

| » | Digital Bits DX0..7, output | Pins 1 & 3 closed |

| Digital Bits DX0..7, input | Open |

|

| » | Digital Bits DX8..15, input | Pins 2 & 4 closed |

| Digital Bits DX8..15, output | Open |

|

PARALLEL I/O PORT SELECTION |

||

Setting |

JP14 |

|

| » | Digital Bits DX0..7, Readback enable | Pins 1 & 2 closed |

| Digital Bits DX0..7, External Digital Clock | Open |

|

| » | Digital Bits DX8..15, Readback enable | Pins 1 & 2 closed |

| Digital Bits DX8..15, External Digital Clock | Open |

|