.

.

ADVANTECH CO., LTD.

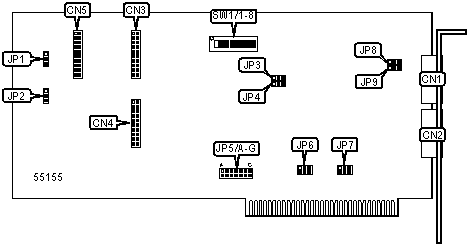

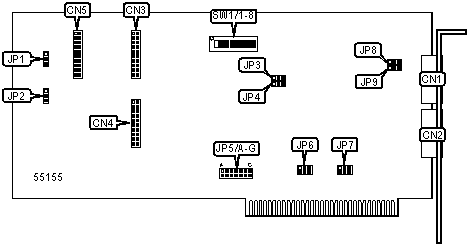

PCL-812PG

|

Card Type |

Dynamic signal acquisition converter |

|

Chip Set |

Intel |

|

Maximum Onboard Memory |

Unidentified |

|

I/O Options |

20-pin termination connectors (5) |

|

Data Bus |

8-bit ISA |

|

Card Size |

Full-length, full-height |

.

.

|

CONNECTIONS |

|||

|

Function |

Label |

Function |

Label |

|

Analog I/O connector 1 |

CN1 |

Digital in |

CN4 |

|

Analog I/O connector 2 |

CN2 |

Counter connector |

CN5 |

|

Digital out |

CN3 |

||

|

USER CONFIGURABLE SETTINGS |

||

|

Function |

Label |

Position |

|

Internal on-board programmable pacer |

JP1 |

Pins 1 & 2 closed |

|

External pulse signal |

JP1 |

Pins 2 & 3 closed |

|

Internal 2MHz clock |

JP2 |

Pins 1 & 2 closed |

|

External clock |

JP2 |

Pins 2 & 3 closed |

|

D/A analog output internal reference voltage set at –10V |

JP8 |

Pins 1 & 2 closed |

|

D/A analog output internal reference voltage set at –5V |

JP8 |

Pins 2 & 3 closed |

|

A/D analog input maximum input voltage set at +/- 10V |

JP9 |

Pins 1 & 2 closed |

|

A/D analog input maximum inout voltage set at +/- 5V |

JP9 |

Pins 2 & 3 closed |

|

WAIT STATE SELECTION |

||

|

Setting |

SW1/7 |

SW1/8 |

|

0 |

On |

On |

|

2 |

Off |

On |

|

4 |

On |

Off |

|

6 |

Off |

Off |

|

DMA CHANNEL SELECTION |

||

|

Channel |

JP6 |

JP7 |

|

1 |

Pins 1 & 2 closed |

Pins 1 & 2 closed |

|

3 |

Pins 3 & 4 closed |

Pins 3 & 4 closed |

|

Disabled |

Pins 5 & 6 closed |

Pins 5 & 6 closed |

|

Note: Pins designated are in the closed position. |

||

|

BASE I/O ADDRESS SELECTION |

||||||

|

Setting |

SW1/1 |

SW1/2 |

SW1/3 |

SW1/4 |

SW1/5 |

SW1/6 |

|

200h |

On |

On |

On |

On |

On |

On |

|

210h |

On |

On |

On |

On |

Off |

On |

|

220h |

On |

On |

On |

Off |

On |

On |

|

240h |

On |

On |

Off |

On |

On |

On |

|

280h |

On |

Off |

On |

On |

On |

On |

|

300h |

Off |

On |

On |

On |

On |

On |

|

380h |

Off |

Off |

On |

On |

On |

On |

|

3C0h |

Off |

Off |

Off |

On |

On |

On |

|

3E0h |

Off |

Off |

Off |

Off |

On |

On |

|

3F0h |

Off |

Off |

Off |

Off |

Off |

On |

|

Note: A total of 255 base address settings are available. The switches are a binary representation of the decimal memory addresses. SW1/6 is the Least Significant Bit and switch SW1/1 is the Most Significant Bit. The switches have the following decimal values: SW1/6=16, SW1/5=32, SW1/4=64, SW1/3=128, SW1/2=256, SW1/1=512. Turn off the switches and add the values of the switches to obtain the correct memory address. (Off=1, On=0) |

||||||

|

INTERRUPT SELECTION |

|||||||

|

IRQ |

JP5/A |

JP5/B |

JP5/C |

JP5/D |

JP5/E |

JP5/F |

JP5/G |

|

IRQ2 |

Closed |

Open |

Open |

Open |

Open |

Open |

Open |

|

IRQ3 |

Open |

Closed |

Open |

Open |

Open |

Open |

Open |

|

IRQ4 |

Open |

Open |

Closed |

Open |

Open |

Open |

Open |

|

IRQ5 |

Open |

Open |

Open |

Closed |

Open |

Open |

Open |

|

IRQ6 |

Open |

Open |

Open |

Open |

Closed |

Open |

Open |

|

IRQ7 |

Open |

Open |

Open |

Open |

Open |

Closed |

Open |

|

Disabled |

Open |

Open |

Open |

Open |

Open |

Open |

Closed |

|

D/A REFERENCE SOURCE SELECTION |

|||

|

Channel 1 |

Channel 2 |

JP3 |

JP4 |

|

Internal |

Internal |

Pins 1 & 2 |

Pins 1 & 2 |

|

External |

External |

Pins 2 & 3 |

Pins 2 & 3 |

|

Internal |

External |

Pins 1 & 2 |

Pins 2 & 3 |

|

External |

Internal |

Pins 2 & 3 |

Pins 1 & 2 |